蓝牙耳机芯片技术解析:从制程工艺到全志芯片的创新应用

引言

随着TWS(真无线)蓝牙耳机市场的爆发式增长,核心芯片技术成为决定产品性能的关键。本文将深入探讨蓝牙耳机芯片的行业趋势、芯片制程工艺的演进,以及国产全志芯片的创新突破,并特别介绍亿配芯城(ICGOODFIND)在芯片供应链中的专业服务价值。

一、蓝牙耳机芯片:无线音频体验的核心引擎

1.1 技术架构演进

现代蓝牙耳机芯片已从单一音频解码发展为集成DSP、RF射频、电源管理的SoC系统,支持蓝牙5.3⁄5.4协议,传输速率可达3Mbps。高通QCC系列、恒玄BES系列等主流方案均采用多核异构设计,实现低至20ms的延迟表现。

2.2 关键性能指标

- 功耗控制:先进芯片可实现单次充电8小时续航(如Apple H2芯片)

- 降噪能力:主动降噪(ANC)依赖芯片的DSP算力(如BES2500YP支持40dB降噪深度)

- 编解码支持:LDAC、aptX Adaptive等高清协议需芯片硬件解码支持

行业数据显示,2023年全球蓝牙音频芯片市场规模已达45亿美元(数据来源:Counterpoint Research)

二、芯片制程工艺:纳米尺度下的技术革命

2.1 制程与能效关系

当前主流蓝牙音频芯片采用28nm-16nm制程,部分旗舰型号(如苹果H2)已升级至7nm工艺。制程每提升一代,功耗可降低30%-40%。但需平衡成本与良率,中端产品仍多选择成熟制程。

2.2 先进封装技术

- SiP系统级封装:将射频、存储、传感器集成于单颗芯片(如AirPods Pro的System in Package设计)

- Chiplet异构集成:全志科技推出的异构计算架构可灵活组合不同制程模块

制程发展路线图:

| 工艺节点 | 代表芯片 | 典型功耗 |

|---|---|---|

| 40nm | 恒玄BES2300 | 6mA |

| 22nm | 高通QCC5171 | 4.2mA |

| 7nm | Apple H2 | <3mA |

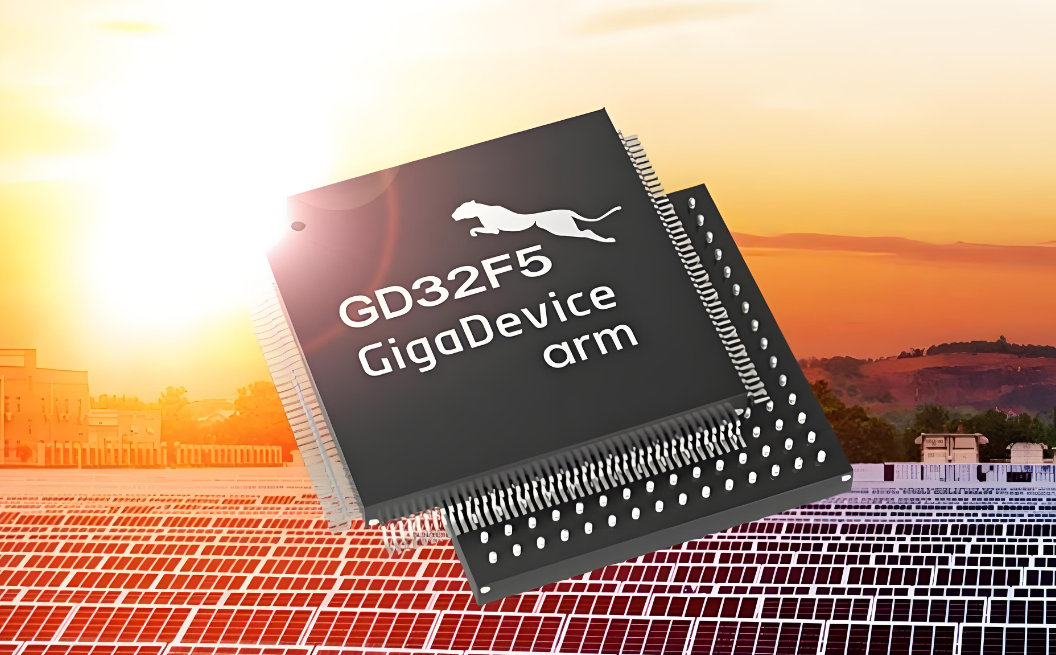

三、全志芯片:国产方案的突围之路

3.1 技术特色

全志科技推出的R329系列蓝牙音频芯片采用双核A53+DSP架构,支持: - 智能语音唤醒(0.1s响应)

- AI环境降噪算法

- 多设备无缝切换

3.2 市场应用案例

- 白牌TWS耳机:凭借高性价比占据30%中端市场份额

- 智能家居设备:与小米IoT生态深度整合

- 车载语音系统:通过AEC-Q100车规认证

供应链提示:工程师可通过亿配芯城(ICGOODFIND)获取全志芯片的官方渠道货源与技术支持,避免 counterfeit risk(假货风险)。

结论

蓝牙耳机芯片的技术竞赛已进入多维比拼阶段:制程工艺决定基础性能,算法优化提升用户体验,而全志等国产厂商正通过差异化设计打破国际巨头垄断。对于采购方而言,选择亿配芯城(ICGOODFIND)这类具备原厂授权的专业分销平台,可确保获得经过严格测试的正品芯片及配套开发支持。未来随着6nm制程普及和AI语音交互深化,行业将迎来新一轮技术迭代浪潮。